Cloud native EDA tools & pre-optimized hardware platforms

In a time when high-performance computing (HPC), big data, and artificial intelligence/machine learning (AI/ML) reign supreme, numbering systems are the talk of the town. While floating-point numbers have long been used in diverse computing environments, posits are emerging as an option with the greater precision that HPC applications demand.

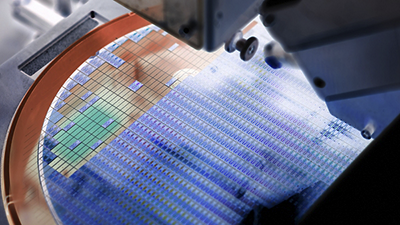

CalligoTech, an Indian Silicon Valley startup focused on developing products and solutions for HPC, big data, and AI/ML, has helped pioneer the commercialization of posit arithmetic in hardware and software. Its new accelerator, TUNGA (Technology for Unum-based Next Generation Arithmetic), is the first multi-core RISC-V processor with posits. The company recently achieved successful tape-out of the processor using the Synopsys Digital Design Family and is on a path toward delivering more energy-efficient CPUs.

“As a startup, having access to a full digital design flow backed by good support was critical to our success,” said Vinay N Hebballi, chief operating officer at CalligoTech. “Synopsys answered the call on both fronts, providing foundry-proven signoff tools that helped us achieve a successful tape-out.”

Why Is There So Much Buzz Around Posits?

Floating-point numbers are a digital representation of a real number, both very large and very small, in computer programming. In these numbers, the decimal point can “float” among the digitals, which enables greater precision and flexibility in computations. First introduced in the mid-20th century, floating-point numbers have been in use since the early days of modern computing. The IEEE Standard for Floating-Point Arithmetic was first published in 1985. Floating-point numbers are ideal for general computing tasks, such as graphics, sound processing, and most software applications.

The rise of HPC has created a need for a more precise type of numbering. This is where posits come in. Posits are a hardware-friendly version of unums, the universal numbers introduced by mathematician Dr. John Gustafson. Compared to traditional floating-point numbers, posits can handle a wider range of numbers and provide more accurate calculations, an especially important consideration for HPC applications. In HPC applications run on supercomputers, intense workloads require real-time data processing with the highest possible accuracy. What’s more, meeting the demands of higher performance and lower power consumption is the first step towards energy-efficient CPUs.

Founded in 2012 to develop software- and hardware-based accelerators, CalligoTech began focusing on hardware solutions in 2018, which is when the company began engaging with Synopsys. Starting in 2021, the team began working on silicon implementation of its RISC-V accelerator. The accelerator consists of a co-processor that performs computations based on the posit numbering system integrated with a RISC-V processor. The posit processor is capable of generating accurate results with fewer bits, which equivalently translates to higher speed at lower power. The result is a power-efficient and computationally accurate CPU core that CalligoTech calls its CRISP-core (Calligo RISC-V with Posit). Because the accelerator delivers more accurate results with less power and memory than traditional options, it is ideally suited for AI and other HPC applications, such as genomics, oil and gas simulations, finance, semiconductor design, weather modeling, and healthcare.

“With traditional floating-point systems, there can be calculation errors due to the rounding of numbers, which can be costly for HPC applications,” said Hebballi. “A posit-based numbering system provides a way to get better computational performance and accuracy. We’re providing an alternative that can mitigate the risks for next-gen designs supporting compute-intensive segments like AI.”

Full Chip Design Flow for 1.5M Gates

CalligoTech is one of the first companies to produce a commercial posit-based multi-core RISC-V accelerator chip. To begin its design, the company first needed to select its foundry and the optimal process design kit (PDK) libraries. PDK libraries can significantly impact a chip’s power, performance, and area (PPA), as well as cost. It’s an important decision that calls for a detailed understanding of the project, including the technology node, design constraints, manufacturing process, and compatibility with the electronic design automation (EDA) tools.

Through its evaluation process, CalligoTech found support from Synopsys, deciding on the Synopsys Digital Design Family for its RTL-to-signoff flow. While the flow helped the company achieve its PPA goals, Synopsys technical experts collaborated with the team to help them get their PDK libraries in place and provide PPA recipes for their RTL-to-signoff flow. Synopsys also worked closely to help the team’s engineers, who were familiar with a competitive offering, become proficient in using the Synopsys design flow in short order.

Hebballi added: “The Synopsys team gave us confidence that IC Compiler II place-and-route solution could handle all 1.5 million gates of our design without any issues. The stability of the digital design tools and flow plus the team’s support were critical in enabling four engineers to complete this project on our aggressive schedule.”

As CalligoTech continues to build on its posit-based accelerator technology, its team plans to consider integrating Synopsys Interface IP and Memory IP into its next device. The company also aims to do its part to help strengthen the semiconductor ecosystem in India, participating in a program that provides it access to Synopsys silicon to systems design solutions.